# EVAL-ADP1047/ADP1048-GUI-RG

# ADP1047/ADP1048 Evaluation Software Reference Guide

#### **GENERAL DESCRIPTION**

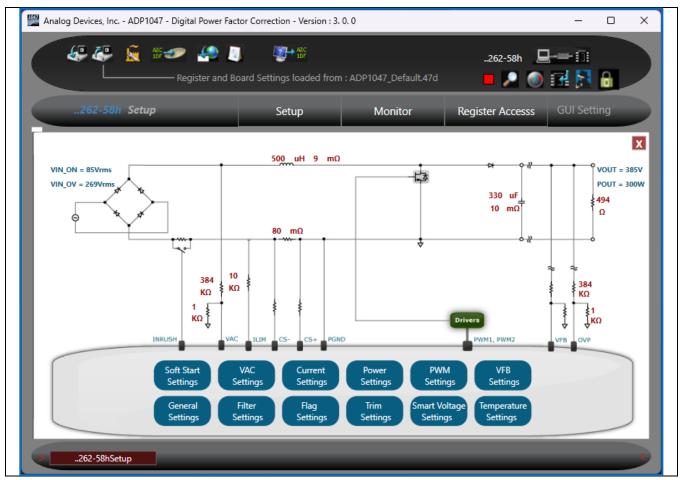

The EVAL-ADP1047/ADP1048-GUI-RG user guide describes the various controls and indicators of the ADP1047/ADP1048 evaluation software. It details the functionality of the GUI button for the register being updated along with a brief description.

Figure 1. GUI Main Interface Window

**DOCUMENT FEEDBACK TECHNICAL SUPPORT** Rev. B; 01/25

# **TABLE OF CONTENTS**

| GENERAL DESCRIPTION           |   |

|-------------------------------|---|

| GUI Controls                  | 3 |

| Link                          | 3 |

| Structural Navigation         | 4 |

| Windows Navigation            | 4 |

| Tools                         |   |

| Dashboard                     |   |

| SETUP                         |   |

| Main (ADP1047 Only)           |   |

| Main (ADP1048 Only)           |   |

| Soft-Start Settings           |   |

| VAC Settings                  |   |

| Current Settings              |   |

| Power Settings (ADP1047 Only) |   |

| Power Settings (ADP1048 Only) |   |

| PWM Settings (ADP1047 Only)   |   |

|                               |   |

|    | FWM Settings (ADF1046 Only) | . 20 |

|----|-----------------------------|------|

|    | VFB Settings                | . 22 |

|    | General Settings            | . 24 |

|    | Filter Settings             | .26  |

|    | Flag Settings               | . 29 |

|    | Trim Settings               | .31  |

|    | Smart Voltage Settings      | . 32 |

|    | Temperature Settings        | . 34 |

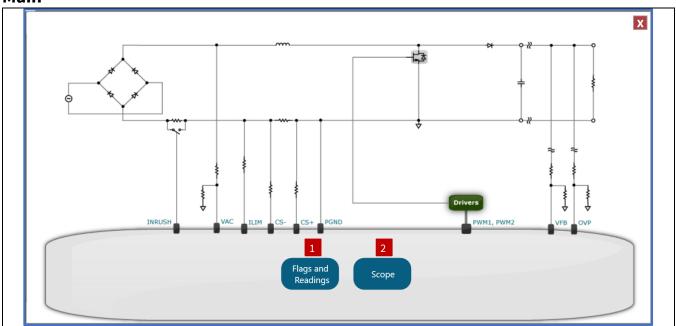

| М  | ONITOR                      | . 35 |

|    | Main                        | .35  |

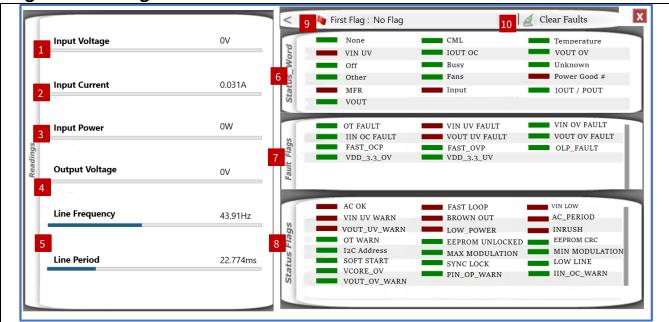

|    | Flags and Readings          | .36  |

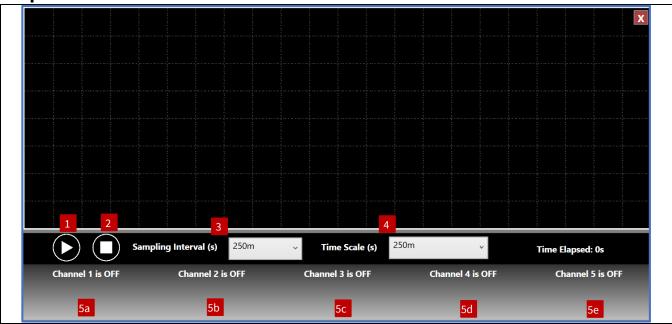

|    | Scope                       | .40  |

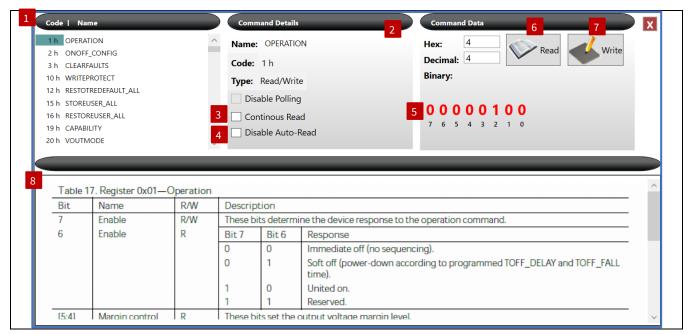

| RE | EGISTER ACCESS              | 41   |

|    | Main                        | 41   |

| Re | evision History             | 42   |

# **GUI CONTROLS**

### Link

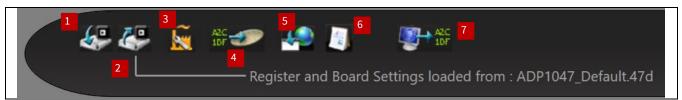

Figure 2. Link Navigation

# Table 1. Figure 2 Callouts

| NO. | NAME                               | REG            | BITS  | R/W     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                |

|-----|------------------------------------|----------------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | USB to I2C<br>Interface<br>Number  |                |       |         | Shows the last three digits of the <i>USB to I2C Interface</i> connected to ADP1047/ADP1048. This number is physically printed on the <b>USB to I2C Interface</b> .                                                                                                                                                                                        |

| 2   | ADP ADP1047/<br>ADP1048<br>Address |                |       |         | Shows to which address of the ADP1047/ADP1048 the GUI is connected.                                                                                                                                                                                                                                                                                        |

| 3   | Communication<br>Link              |                |       |         | Shows whether the GUI is communicating with the ADP1047/ADP1048.                                                                                                                                                                                                                                                                                           |

| 4   | PSON Status<br>Indicator           |                |       |         | Indicates the state of PSON operation command; red = off, green = on.                                                                                                                                                                                                                                                                                      |

| 5   | Scan                               |                |       |         | Scans for all ADP1047/ADP1048 devices connected to the computer. This function helps connect and disconnect devices once the GUI is running.                                                                                                                                                                                                               |

| 6   | Dashboard                          |                |       |         | Opens the <i>Dashboard</i> window.                                                                                                                                                                                                                                                                                                                         |

| 7   | Update EEPROM                      | 0xD5           | [7:0] | W       | Writes the contents of the registers to the EEPROM of ADP1047/ADP1048.                                                                                                                                                                                                                                                                                     |

|     |                                    | 0xFE81<br>0x15 | [6]   | RO<br>W | This is accomplished by writing password twice to register 0xD5 (default is 0h) to unlock the EEPROM. The unlocking status can be checked by reading register 0xFE81 bit 6, which is followed by issuing a 0x15 command to write the contents to the EEPROM. Wait 40ms, then lock the EEPROM by writing any byte other than the password on register 0xD5. |

| 8   | Spy                                |                |       |         | Opens the <i>Spy</i> window.                                                                                                                                                                                                                                                                                                                               |

| 9   | Lock/Unlock                        | 0xD6           | [7:0] | W       | Locks or unlocks write access for Trim registers.                                                                                                                                                                                                                                                                                                          |

|     |                                    | 0xFE37         | [7:0] | R/W     |                                                                                                                                                                                                                                                                                                                                                            |

analog.com Rev. B 3 of 43

# **Structural Navigation**

Figure 3. Structural Navigation

### **Table 2. Figure 3 Callouts**

| NO. | NAME                     | REG | BITS | R/W | DESCRIPTION                                                                                                                                                                                                                 |

|-----|--------------------------|-----|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Device Window<br>Info    |     |      |     | Shows the device address and the name of the window that is currently open.                                                                                                                                                 |

| 2   | Structural<br>Navigation |     |      |     | If only one device is connected to the GUI, clicking the buttons opens the respective windows. If multiple devices are connected, clicking the buttons opens the window for the device selected in the <i>Link</i> section. |

# **Windows Navigation**

**Table 3. Figure 4 Callouts**

| NO. | NAME   | REG | BITS | R/W | DESCRIPTION                                                     |

|-----|--------|-----|------|-----|-----------------------------------------------------------------|

| 1   | Arrows |     |      |     | Moves the tabs in their respective directions.                  |

| 2   | Tabs   |     |      |     | Opens the window on whose name and device address is displayed. |

analog.com Rev. B 4 of 43

# **Tools**

Figure 5. Tools Navigation

### **Table 4. Figure 5 Callouts**

| NO. | NAME                                | REG | BITS | R/W | DESCRIPTION                                                                                                                                                                                 |

|-----|-------------------------------------|-----|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Save Register and<br>Board Settings |     |      |     | Saves the contents of the register map and the board settings (external components) from the device selected in the <i>Link</i> section to either a <b>.47d</b> file or a <b>.48d</b> file. |

| 2   | Load Register and<br>Board Settings |     |      |     | Loads the contents of the register map and the board settings (external components) to the device selected in the <i>Link</i> section from either a <b>.47d</b> file or a <b>.48d</b> file. |

| 3   | Load Factory-<br>Trim Values        |     |      |     | Loads the factory trim settings to the part.                                                                                                                                                |

| 4   | EEPROM Access                       |     |      |     | Opens a page to access pages 4 to 15 of the EEPROM. These pages can be used to save any user-defined information.                                                                           |

| 5   | Update GUI                          |     |      |     | Connects to Analog Devices and redirects to the page that contains the latest version of the GUI.                                                                                           |

| 6   | Reference Guide                     |     |      |     | Opens the GUI Reference Guide.                                                                                                                                                              |

| 7   | Generate HEX File                   |     |      |     | Generates a HEX file of the register map for use in a production environment.                                                                                                               |

analog.com Rev. B 5 of 43

# **Dashboard**

Figure 6. Dashboard Navigation

# Table 5. Figure 6 Callouts

| NO. | NAME    | REG    | BITS   | R/W | DESCRIPTION                                                                                    |

|-----|---------|--------|--------|-----|------------------------------------------------------------------------------------------------|

| 1   | PS ON   | 0x01   | [7]    | R/W | Sets the device response to the operation command.                                             |

| 2   | IPV     | 0x88   | [15:0] | R   | Displays the input voltage (V) in VIN linear mode format.                                      |

| 3   | IPP     | 0x89   | [15:0] | R   | Displays the input current (A) in current linear mode format.                                  |

| 4   | OPV     | 0x97   | [15:0] | R   | Displays the input power (W) in power linear mode format.                                      |

| 5   | VOUT OV | 0x7A   | [7]    | R   | Red = The output voltage is above the OUT_OV_FAULT_LIMIT.                                      |

| 6   | VIN UV  | 0x78   | [3]    | R   | Red = General input undervoltage fault.                                                        |

| 7   | IIN OC  | 0xFE99 | [2]    | R   | Red = The input current measured on the CS ADC is larger than the value in IIN_OC_FAULT_LIMIT. |

analog.com Rev. B 6 of 43

### **SETUP**

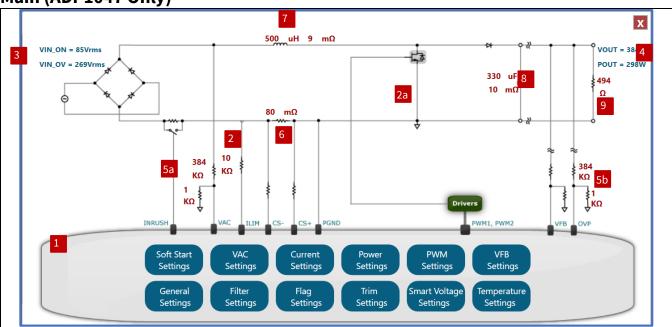

# Main (ADP1047 Only)

Figure 7. Single-Phase PFC

#### **Table 6. Figure 7 Callouts**

| NO. | NAME                          | REG    | BITS | R/W | DESCRIPTION                                                                                                                                                                             |

|-----|-------------------------------|--------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ADP1047 Setup<br>Blocks       |        |      |     | The grey block represents the ADP1047, and the blue blocks represent the various setup blocks of the ADP1047. Click the blue blocks to open the settings for the corresponding windows. |

|     |                               |        |      |     | The components outside the ADP1047 represents the simplified power diagram connections needed for PFC operation and loop-compensation calculations.                                     |

| 2   | ILIM (Fast OC) Setting Source | 0xFE3E | [7]  | R/W | Sets the fast overcurrent ILIM setting either from the sense resistor [6] (negative level shifting current source) or source                                                            |

| 2a  | Resistor                      |        |      |     | resistor [2a] (positive level shifting current source). Together with the ILIM resistor value, the fast OC level can be set accordingly in the <i>Current Settings</i> block.           |

| 3   | Input<br>Parameters           | 0x35   | [16] | R/W | VIN_ON (AC turn on voltage) and VIN_OV (AC overvoltage level) are shown to provide the designed input operating range the PFC circuit.                                                  |

|     |                               | 0x55   | [16] | R/W | Use the <b>VAC Settings</b> block to update these parameters.                                                                                                                           |

analog.com Rev. B | 7 of 43

# **EVAL-ADP1047/ADP1048-GUI-RG**

| 4        | Output<br>Parameters                                  | 0x21 | [16] | R/W | VOUT (output voltage) and POUT (output power) are shown to provide a quick reference on the designed nominal output voltage and power of the PFC circuit.  Use the <b>VFB Settings</b> block to configure the VOUT. Update POUT with the load resistor [9].                                |

|----------|-------------------------------------------------------|------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5a<br>5b | Input Voltage<br>Divider<br>Output Voltage<br>Divider |      |      |     | External resistor dividers are needed to bring the input and output signals to the operating range of the ADC (0V to 1.6V). The default values ratio of $384k\Omega$ and $1k\Omega$ provide ~1V on the input pins VAC, VFB, and OVP, which work in most application in the < $500V$ range. |

| 6        | Current-Sense<br>Resistor                             |      |      |     | Controls, protects, and monitors the PFC stage.                                                                                                                                                                                                                                            |

| 7        | Inductor                                              |      |      |     | Sets the value of the PFC inductor and the DCR value. Use the loaded inductance value for more accurate loop compensation.                                                                                                                                                                 |

| 8        | Output Bulk<br>Capacitors                             |      |      |     | Sets the value of the output bulk capacitors and the ESR value. The capacitor value is based on the hold-up time requirement.                                                                                                                                                              |

| 9        | Load Resistor                                         |      |      |     | Set the equivalent resistance value for the nominal power rating (e.g., $POUT = VOUT^2/R_{LOAD}$ ).                                                                                                                                                                                        |

analog.com Rev. B 8 of 43

#### 500 uH 9 mΩ VIN ON = 85Vrms 247 10 11 10 8a κΩ ΚΩ 8b 1 ΚΩ ... PWM Settings VFB Settings Flag Settings mart Voltage Temperature Settings х 500 uH 9 mΩ T2 C 660 uF <sup>247</sup> Ω 11 10 7a <sub>385</sub> 6 VIN OV = 270Vrms POUT = 600W ΚΩ ΚΩ 3 8b **1** ΚΩ 10 ΚΩ Settings Settings mart Voltage Settings Temperature

# Main (ADP1048 Only)

Figure 8. Interleaved PFC (Top) and Bridgeless PFC (Bottom)

**Table 7. Figure 8 Callouts**

| NO. | NAME                    | REG    | BITS | R/W | DESCRIPTION                                                                                                                                                                                                                                                                                                                               |

|-----|-------------------------|--------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ADP1048 Setup<br>Blocks |        |      |     | The grey block represents ADP1048 and the blue blocks represent the various setup blocks of the ADP1048. These blue blocks can be clicked to open the corresponding windows for settings.  The components outside ADP1048 represents the simplified power diagram connection needed for PFC operation and loop-compensation calculations. |

| 2   | ADP1048<br>Operation    | 0xFE14 | [4]  | R/W | Sets either interleaved PFC operation (first diagram) or bridgeless PFC operation (second diagram).                                                                                                                                                                                                                                       |

Rev. B 9 of 43 analog.com

| 3  | ILIM (Fast OC)<br>Setting     | 0xFE3E | [7]  | R/W | Sets the fast overcurrent ILIM setting. For interleaved PFC, connect ILIM to either the sense resistor [7] or the source resistor [4]. For bridgeless PFC, connect through the current transformer sense resistor [7] for ground isolation. Together with the ILIM resistor value, use the <i>Current Settings</i> block to set the fast OC level accordingly. |

|----|-------------------------------|--------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4  | IBAL Pin/<br>Source Resistor  |        |      |     | For interleaved PFC operation, the source resistor connected to the IBAL pin is also used in maintaining current balance between the interleaved phases.                                                                                                                                                                                                       |

|    |                               |        |      |     | For bridgeless PFC operation, use the IBAL pin to detect zero-<br>crossing to synchronize the active power rail to the AC line<br>phase.                                                                                                                                                                                                                       |

| 5  | Input<br>Parameters           | 0x35   | [16] | R/W | VIN_ON (AC turn on voltage) and VIN_OV (AC overvoltage level) are shown to provide the designed input operating range the PFC circuit.                                                                                                                                                                                                                         |

|    |                               | 0x55   | [16] | R/W | Use the <b>VAC Settings</b> block to update these parameters.                                                                                                                                                                                                                                                                                                  |

| 6  | Output<br>Parameters          | 0x21   | [16] | R/W | VOUT (output voltage) and POUT (output power) are shown to provide a quick reference on the designed nominal output voltage and power of the PFC circuit.  Configure VOUT on the <i>VFB Settings</i> block. Update POUT with the load resistor [11].                                                                                                           |

| 7  | Current-Sense<br>Resistor     |        |      |     | The current-sense resistor is used for control, protection, and monitoring of the PFC stage.                                                                                                                                                                                                                                                                   |

| 7a | Current-Sense<br>Transformers |        |      |     | For bridgeless PFC operation, use current transformers to simplify the sensing and to minimize power dissipation.                                                                                                                                                                                                                                              |

| 8a | Input Voltage<br>Divider      |        |      |     | External resistor dividers are needed to bring the input and output signals within the operating range of the ADC (0V to 1.6V).                                                                                                                                                                                                                                |

| 8b | Output Voltage<br>Divider     |        |      |     | The default values ratio of $384k\Omega$ and $1k\Omega$ provide ~1V on the input pins VAC, VFB, and OVP. They work in most application in < 500V range.                                                                                                                                                                                                        |

| 9  | Inductors                     |        |      |     | Sets the value of the PFC inductors and the DCR values. Use the loaded inductance value for more accurate loop compensation.                                                                                                                                                                                                                                   |

| 10 | Output Bulk<br>Capacitors     |        |      |     | Sets the value of the output bulk capacitors and the ESR value. The capacitor value is based on the hold-up time requirement.                                                                                                                                                                                                                                  |

| 11 | Load Resistor                 |        |      |     | Sets the equivalent resistance value for the nominal power rating (e.g., $POUT = VOUT^2/R_{LOAD}$ ).                                                                                                                                                                                                                                                           |

analog.com Rev. B 10 of 43

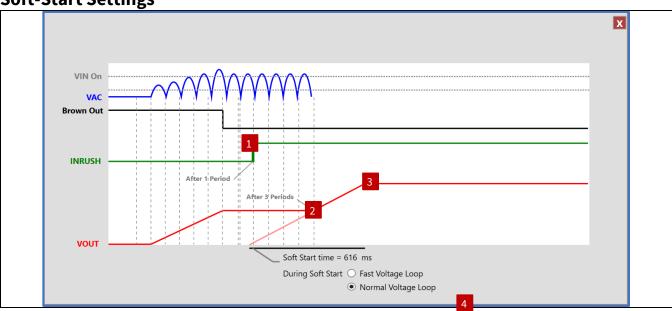

**Soft-Start Settings**

Figure 9. Soft-Start Navigation

### **Table 8. Figure 9 Callouts**

| NO. | NAME                                     | REG    | BITS  | R/W | DESCRIPTION                                                                                                                                                                                                           |

|-----|------------------------------------------|--------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Inrush Delay                             | 0xFE2E | [2:0] | R/W | Sets the inrush signal delay time after the BROWN_OUT flag goes low (0 to 7 AC cycles after brownout).  Delay time allows the output bulk capacitor to charge to peak AC voltage through the NTC/PTC inrush resistor. |

| 2   | Soft-Start Delay<br>Time                 | 0xFE2D | [5:3] | R/W | Sets the delay time between the inrush signal and the origin of the soft start (0 to 7 AC cycles after brownout).                                                                                                     |

| 3   | Sof-Start Time                           | 0xFE2D | [2:0] | R/W | Sets the ramp-up time of the output: 112ms, 168ms 224ms, 280ms, 392ms, 504ms, 616ms, 728ms                                                                                                                            |

| 4   | Enable Fast<br>Loop during<br>Soft Start | 0xFE24 | [1]   | R/W | Enables either <i>Fast Voltage Loop</i> or <i>Normal Voltage Loop</i> by clicking one of the buttons.                                                                                                                 |

analog.com Rev. B 11 of 43

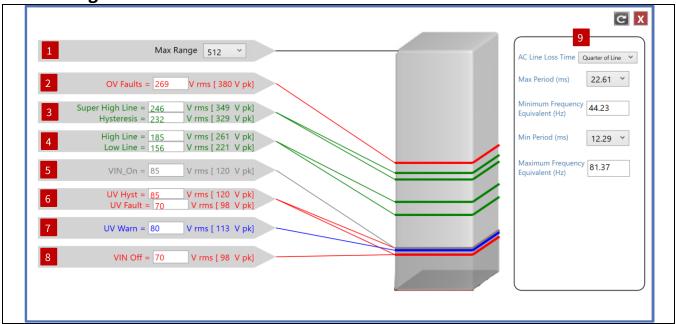

# **VAC Settings**

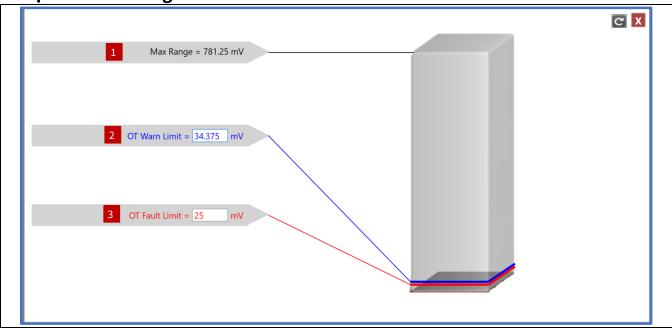

Figure 10. VAC Settings Navigation

#### Table 9. Figure 10 Callouts

| NO. | NAME                   | REG    | BITS    | R/W | DESCRIPTION                                                                                                                                                                                                              |

|-----|------------------------|--------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Max Range              | 0xFE39 | [5:3]   | R/W | This sets the exponent for the input voltage. Supported Max Range are 256, 512, and 1024.                                                                                                                                |

|     |                        | 0x55   | [15:0]  | R/W | The voltage value in RMS is calculated using the linear mode                                                                                                                                                             |

|     |                        | 0x35   | [15:0]  | R/W | format V = Y * 2 <sup>N</sup> , where Y is the mantissa using the lower 11                                                                                                                                               |

|     |                        | 0x36   | [15:0]  | R/W | bits [10:0] and N is the 2-s complement of the upper 3 bits                                                                                                                                                              |

|     |                        | 0x58   | [15:0]  | R/W | [13:11].                                                                                                                                                                                                                 |

|     |                        | 0x59   | [15:0]  | R/W |                                                                                                                                                                                                                          |

| 2   | OV Fault<br>Exponent N | 0x55   | [13:11] | R   | Sets the upper volt measured at the PFC input voltage that causes an overvoltage fault condition.                                                                                                                        |

|     | Mantissa               |        | [10:0]  | R/W | To set the value, either directly input the value or use the slider. Press <i>Enter</i> to confirm value change.                                                                                                         |

| 3   | Super High<br>Line     | 0xFE4B | [10:0]  | R/W | Sets the input voltage value as a super high line limit for smart output voltage feature. Register value is ~6.65 * V <sub>RMS</sub>                                                                                     |

|     | Hysteresis             | 0xFE4D | [7:0]   | R/W | This sets the voltage hysteresis of the super high line voltage for the smart output voltage operation. The voltage delta is limited to 38V. Register value is $\sim$ (SuperHighLine-Hysteresis)V <sub>RMS</sub> * 6.65. |

analog.com Rev. B | 12 of 43

|   | 1                                  |        |                   |          |                                                                                                                                       |

|---|------------------------------------|--------|-------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| 4 | High Line                          | 0xFE35 | [7:0]             | R/W      | This sets the high line limit. When the input voltage is higher than this value, the current loop filter for high line input is used. |

|   | Low Line                           | 0xFE36 | [7:0]             | R/W      | Register value is ~V <sub>RMS</sub> /2.40.                                                                                            |

|   |                                    |        |                   |          | This sets the low line limit. When the input voltage is lower than this value, the current loop filter for low input is used.         |

|   |                                    |        |                   |          | Register value is ~V <sub>RMS</sub> /2.40.                                                                                            |

| 5 | VIN On<br>Exponent N               | 0x35   | [13:11]           | R        | Sets the value of the input voltage to start power conversion.                                                                        |

|   | Mantissa                           |        | [10:0]            | R/W      |                                                                                                                                       |

| 6 | UV Fault<br>Exponent N<br>Mantissa | 0x59   | [13:11]<br>[10:0] | R<br>R/W | Sets the upper voltage measured at the PFC input voltage that causes an undervoltage fault condition.                                 |

|   | UV Hysteresis                      | 0xFE51 | [7:0]             | R/W      | Register value is ~(UV Hysteresis – UV Fault)V <sub>RMS</sub> * 4.0.                                                                  |

| 7 | UV Warn<br>Exponent N              | 0x58   | [13:11]           | R        | Sets the upper voltage measured at the PFC voltage that causes an undervoltage warning condition.                                     |

|   | Mantissa                           |        | [10:0]            | R/W      |                                                                                                                                       |

| 8 | VIN Off<br>Exponent N              | 0x36   | [13:11]           | R        | Sets the value of the input voltage to stop power conversion.                                                                         |

|   | Mantissa                           |        | [10:0]            | R/W      |                                                                                                                                       |

| 9 | AC Line Loss<br>Time               | 0xFE2E | [4:3]             | R/W      | Sets the timer for the VIN_LOW_FLAG measurement.                                                                                      |

|   | Max Period                         | 0xFE28 | [7:0]             | R/W      | Sets the maximum AC line period of the input voltage.  Equivalent frequency is listed for easy reference.                             |

|   | Min Period                         | 0xFE27 | [7:0]             | R/W      | Sets the minimum AC line period of the input voltage. Equivalent frequency is listed for easy reference.                              |

analog.com Rev. B | 13 of 43

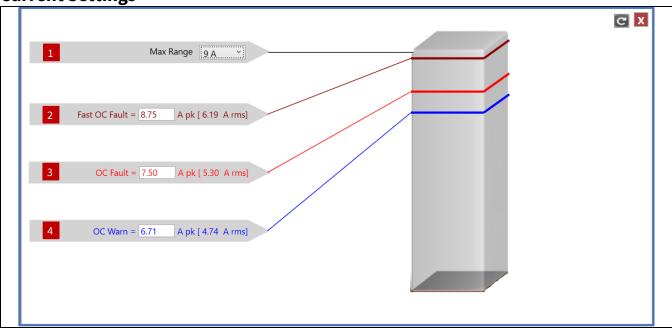

# **Current Settings**

Figure 11. Current Settings Navigation

#### **Table 10. Figure 11 Callouts**

| NO. | NAME                               | REG                              | BITS                                | R/W               | DESCRIPTION                                                                                                                                                                                                                                                                                                                    |

|-----|------------------------------------|----------------------------------|-------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Max Range                          | 0xFE39<br>0x5B<br>0x5D<br>0xFE3E | [10:6]<br>[15:0]<br>[15:0]<br>[6:5] | R/W<br>R/W<br>R/W | Sets the exponent for the input current.  The drop-down menu provides two ranges that correspond to the current-sense ADC voltage ranges: V <sub>ADC</sub> = 500mV or 750mV rounded off.  Max Range = V <sub>ADC</sub> /Current-Sense Resistor  Current-Sense Resistor: See Table 6, item 6.                                   |

| 2   | Fast OC Fault                      | 0xFE3E                           | [6:5]                               | R/W               | Sets the ILIM absolute value.  The value is determined by the discrete ILIM current value and the ILIM resistor. See Table 6, item 2.  To set the value, either directly input the value or use the slider. Press <i>Enter</i> to confirm the value change.                                                                    |

| 3   | OC Fault<br>Exponent N<br>Mantissa | 0x5B                             | [15:11]                             | R<br>R/W          | Sets the accurate overcurrent threshold measured at the PFC input current that causes an overcurrent fault condition.  Current value in RMS is calculated using the linear mode format ( $I = Y * 2^N$ ), where Y is the mantissa that uses the lower 11 bits [10:0], and N is the 2-s complement of the upper 5 bits [15:11]. |

| 4   | OC Warn<br>Exponent N              | 0x5D                             | [15:11]                             | R                 | Sets the accurate overcurrent threshold measured at the PFC input current that causes an overcurrent warning condition.                                                                                                                                                                                                        |

analog.com Rev. B 14 of 43

| Mantissa | [10:0] | R/W | Value stored is in RMS. |

|----------|--------|-----|-------------------------|

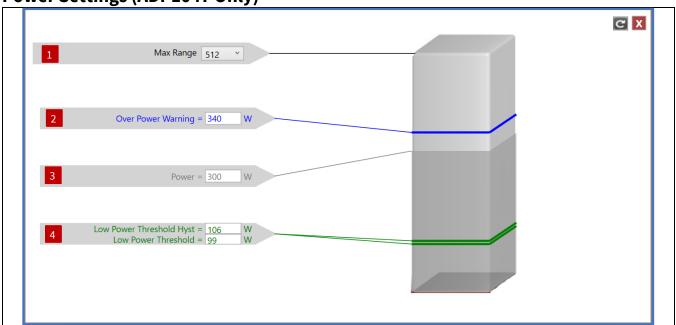

Power Settings (ADP1047 Only)

Figure 12. Power Settings (ADP1047 Only) Navigation

#### **Table 11. Figure 12 Callouts**

| NO. | NAME                                            | REG                                | BITS                              | R/W               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------------------------------------------|------------------------------------|-----------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Max Range                                       | 0xFE39<br>0x6B<br>0xFE32<br>0xFE4E | [2:0]<br>[15:0]<br>[7:0]<br>[7:0] | R/W<br>R/W<br>R/W | Sets the exponent for the input power. Supported Max Range values are 256, 512, 1024, up to 32768.  Before changing this setting, ensure the other values are less than the new Max Range value selected, otherwise, the change will not be applied, and a warning message will be displayed.                                                                                          |

| 2   | Over-Power<br>Warning<br>Exponent N<br>Mantissa | 0x6B                               | [13:11]                           | R<br>R/W          | Sets the value of the input power, in watts, which triggers a warning that the input power is high.  The power value in watts is calculated using the linear mode format (P = Y * 2 <sup>N</sup> ), where Y is the mantissa that uses the lower 11 bits [10:0], and N is the 2-s complement of the upper 3 bits [13:11].  To set the value, either directly input the value or use the |

| 3   | Power                                           |                                    |                                   |                   | slider. Press <i>Enter</i> to confirm value change.  This is the nominal output power of the PFC displayed for quick reference compared to other parameters.                                                                                                                                                                                                                           |

Rev. B 15 of 43 analog.com

|   |                                  |        |       |     | Configure this value through the load resistor, $R_{LOAD}$ , on the main page. See Table 6, item 11, and VOUT in the <b>VFB Settings</b> (e.g., POUT = VOUT <sup>2</sup> / $R_{LOAD}$ ). |

|---|----------------------------------|--------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | Low-Power<br>Threshold<br>Hyster | 0xFE4E | [7:0] | R/W | Sets the power hysteresis for low power mode operation. The register value is the ~PowerDelta/1.4, (e.g., 7/1.4).                                                                        |

|   | Low Power<br>Threshold           | 0xFE32 | [7:0] | R/W | Sets threshold value of the lower power operation detection.<br>Register value is ~Power/1.4, e.g., 106/1.4.                                                                             |

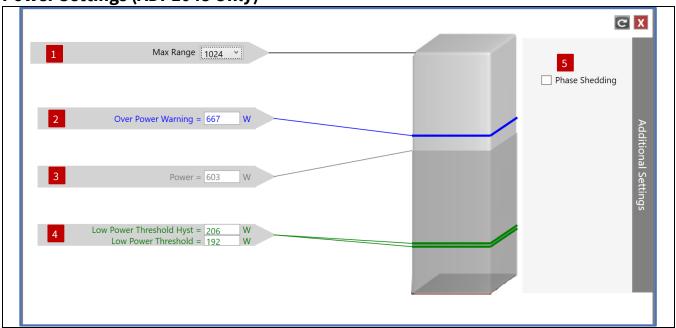

Power Settings (ADP1048 Only)

Figure 13. Power Settings (ADP1048 Only) Navigation

Table 12. Figure 13 Callouts

| NO. | NAME                                            | REG                                | BITS                                | R/W                      | DESCRIPTION                                                                                                                                                                                                                                                                                   |

|-----|-------------------------------------------------|------------------------------------|-------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Max Range                                       | 0xFE39<br>0x6B<br>0xFE32<br>0xFE4E | [2:0]<br>[15:11]<br>[10:0]<br>[7:0] | R/W<br>R/W<br>R/W<br>R/W | Sets the exponent for the input power. Supported Max Range values are 256, 512, 1024, up to 32768.  Before changing this setting, ensure the other values are less than the new Max Range value selected, otherwise, the change will not be applied, and a warning message will be displayed. |

| 2   | Over-Power<br>Warning<br>Exponent N<br>Mantissa | 0x6B                               | [13:11]                             | R<br>R/W                 | Sets the value of the input power, in watts, which triggers a warning that the input power is high.  To set the value, either directly input the value or use the slider. Press <i>Enter</i> to confirm value change.                                                                         |

analog.com Rev. B | 16 of 43

# EVAL-ADP1047/ADP1048-GUI-RG

| 3 | Power                       |        |       |     | This is the nominal output power of the PFC displayed for quick reference compared to other parameters.   Configure this value through the load resistor, $R_{LOAD}$ , on the main page. See Table 6, item 11, and VOUT in the <b>VFB Settings</b> (e.g., POUT = VOUT <sup>2</sup> / $R_{LOAD}$ ). |

|---|-----------------------------|--------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | Low-Power<br>Threshold Hyst | 0xFE4E | [7:0] | R/W | Sets the power hysteresis for low-power mode operation.                                                                                                                                                                                                                                            |

|   | Low-Power<br>Threshold      | 0xFE32 | [7:0] | R/W | The register value is the ~PowerDelta/2.8, (e.g., 14/2.8). This sets the threshold value of the lower power operation detection. The register value is ~Power/2.8 (e.g., 192/2.8).                                                                                                                 |

| 5 | Phase<br>Shedding           | 0xFE4F | [4]   | R/W | Enables or disables phase shedding for interleaved PFC to achieve higher efficiency at lower output power. This feature is not available in bridgeless PFC mode.                                                                                                                                   |

analog.com Rev. B | 17 of 43

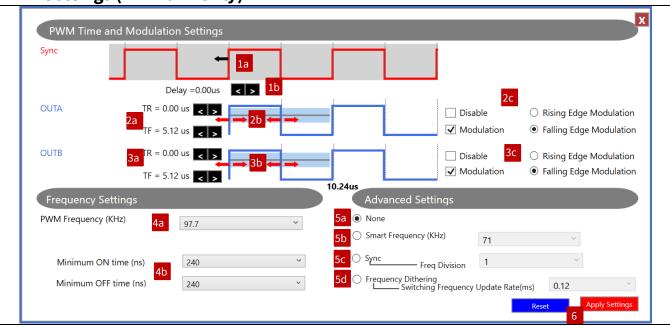

# **PWM Settings (ADP1047 Only)**

Figure 14. PWM Settings (ADP1047 Only) Navigation

#### **Table 13. Figure 14 Callouts**

| NO. | NAME                   | REG    | BITS   | R/W | DESCRIPTION                                                                                                                                                                                             |

|-----|------------------------|--------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1a  | Sync Delay<br>- Slider | 0xFE4C | [15:0] | R/W | Sets the additional delay of the synchronization reference clock to the rising edge of PWM. Adjustments can be made using the slider [1a] for coarser steps or using buttons [1b] for finer adjustment. |

| 1b  | - Buttons              |        |        |     | Step size is 40ns, and value is clamped to 112.5% of the programmed frequency. If desired, enable the synchronization feature in the advanced settings [5c].                                            |

|     | OUTA (PWM)             | 0xFE0C | [7:0]  | R/W | Main PWM OUTA for driving a PFC MOSFET.                                                                                                                                                                 |

| 2a  | - Buttons              | 0xFE0D | [3:2]  | R/W | Adjust both the rising (t1) and falling (t2) PWM edges using                                                                                                                                            |

|     |                        | 0xFE0E | [7:0]  | R/W | buttons [2a] for precise 40ns adjustments or using sliders [2b]                                                                                                                                         |

| 2b  | - Sliders              | 0xFE0F | [3:2]  | R/W | for coarser steps.                                                                                                                                                                                      |

| 2c  | - Configurations       | 0xFE14 | [2:1]  | R/W | Enable or disable the PWM, enable or disable the modulation, and select either leading edge or trailing edge modulation scheme.                                                                         |

|     | OUTB (PWM2)            | 0xFE10 | [7:0]  | R/W | Drives active snubber circuit for a zero-voltage transition,                                                                                                                                            |

| 3a  | - Buttons              | 0xFE11 | [3:2]  | R/W | soft-switched PFC circuit.                                                                                                                                                                              |

|     |                        | 0xFE12 | [7:0]  | R/W | Adjust both rising (t1) and falling (t2) PWM edges using                                                                                                                                                |

| 3b  | - Sliders              | 0xFE13 | [3:2]  | R/W | buttons [2a] for precise 40ns adjustment or using sliders [2b]                                                                                                                                          |

|     |                        | 0xFE14 | [2:1]  | R/W | for coarser steps.                                                                                                                                                                                      |

| 3c  | - Configuration        |        |        |     |                                                                                                                                                                                                         |

analog.com Rev. B | 18 of 43

|    |                                             |                  |              | 1          |                                                                                                                                      |

|----|---------------------------------------------|------------------|--------------|------------|--------------------------------------------------------------------------------------------------------------------------------------|

|    |                                             |                  |              |            | Enable or disable the PWM, enable or disable the modulation, and select either leading edge or trailing edge modulation              |

|    |                                             |                  |              |            | scheme.                                                                                                                              |

|    | Frequency<br>Settings                       | 0xFE1B           |              |            |                                                                                                                                      |

| 4a | PWM Frequency                               | 0xFE15           | [5:0]        | R/W        | Sets the switching frequency between 30kHz to 400kHz.                                                                                |

| 4b | Minimum On<br>Time                          |                  | [7:4]        | R/W        | Sets the minimum on time in 80ns steps from 0ns to 1.2μs.                                                                            |

|    | Minimum Off<br>Time                         |                  | [3:0]        | R/W        | Sets the minimum off time in 80ns steps from 40ns to 1.2μs.                                                                          |

|    | Advanced<br>Settings                        | 0xFE4F           | [7:0]        | R/W        | Advanced feature configuration                                                                                                       |

| 5a | None                                        |                  |              |            | No advanced feature is enabled.                                                                                                      |

| 5b | Smart<br>Frequency                          | 0xFE4F<br>0xFE1C | [3]<br>[5:0] | R/W<br>R/W | Enables smart frequency switching at lower loads to achieve higher efficiency. The frequency value must be lower than PWM frequency. |

| 5c | -Frequency<br>Select                        | 0xFE4F           | [1]<br>[1:0] | R/W<br>R/W | Enables PWM synchronization ( $f_{SW}$ ) with external clock source ( $f_{SYNC}$ ).                                                  |

| 5d | Synchronization<br>- Freq Division          | 0xFE1E           | [0]          | R/W        | Frequency division sets the ratio between $f_{SW}$ and $f_{SYNC}$ .                                                                  |

|    | Frequency                                   | 0xFE4F<br>0xFE1D | [6:0]        | R/W        | Enables frequency dithering for EMI reduction, which varies the switching period by ~±12.5%.                                         |

|    | Dithering - Switching Frequency Update Rate | OXFEID           |              |            | This sets the period for updating the switching frequency in 40μs steps.                                                             |

| 6  | Reset                                       |                  |              |            | Undoes uncommitted changes in simulation mode. If connected to a device, it reloads the programmed settings.                         |

|    | Apply Settings                              |                  |              |            | This button applies all the PWM settings to the part.                                                                                |

analog.com Rev. B | 19 of 43

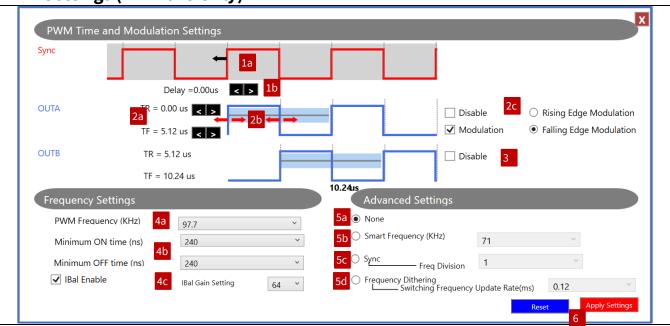

# **PWM Settings (ADP1048 Only)**

Figure 15. PWM Settings (ADP1048 Only) Navigation

#### Table 14. Figure 15 Callouts

| NO.      | NAME                          | REG                        | BITS                    | R/W               | DESCRIPTION                                                                                                                                                                                                             |

|----------|-------------------------------|----------------------------|-------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1a       | Sync Delay<br>- Slider        | 0xFE4C                     | [15:0]                  | R/W               | Sets the additional delay of the synchronization reference clock to the rising edge of PWM. Use the slider [1a] for coarser steps or use the buttons [1b] for finer adjustment.                                         |

| 1b       | - Buttons                     |                            |                         |                   | The step size is 40ns and the value is clamped to 112.5% of the programmed frequency. If desired, enable the synchronization feature in the advanced settings [5c].                                                     |

|          | OUTA (PWM)                    | 0xFE0C                     | [7:0]                   | R/W               | Drives PFC MOSFET.                                                                                                                                                                                                      |

| 2a       | - Buttons                     | 0xFE0D                     | [3:2]                   | R/W               | Adjust both rising (t1) and falling (t2) PWM edges by using                                                                                                                                                             |

| 2b<br>2c | - Sliders<br>- Configurations | 0xFE0E<br>0xFE0F<br>0xFE14 | [7:0]<br>[3:2]<br>[2:1] | R/W<br>R/W<br>R/W | buttons [2a] for precise 40ns adjustments or using the sliders [2b] for coarser steps.  Enable or disable the PWM, enable or disable the modulation, and select either leading edge or trailing edge modulation scheme. |

|          | OUTB (PWM2)                   | 0xFE10                     | [7:0]                   | R/W               | Interleaved PWM2 OUTB for driving MOSFET of the other PFC                                                                                                                                                               |

| 3        | - Configuration               | 0xFE11                     | [3:2]                   | R/W               | phase.                                                                                                                                                                                                                  |

|          |                               | 0xFE12<br>0xFE13<br>0xFE14 | [7:0]<br>[3:2]<br>[2:1] | R/W<br>R/W<br>R/W | For the ADP1048, PWM2 is automatically configured to be 180° out of phase for interleaved and in-phase for bridgeless in relation to OUTA.                                                                              |

analog.com Rev. B | 20 of 43

|    |                                                       |                  |              |            | The only enable or disable option is available for OUTB in the ADP1048.                                                                                                                                                                            |

|----|-------------------------------------------------------|------------------|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Frequency<br>Settings                                 |                  |              |            |                                                                                                                                                                                                                                                    |

| 4a | PWM Frequency                                         | 0xFE1B           | [5:0]        | R/W        | Sets the switching frequency between 30kHz to 400kHz.                                                                                                                                                                                              |

| 4b | Minimum On-<br>Time                                   | 0xFE15           | [7:4]        | R/W        | Sets the minimum on-time in 80ns steps from 0ns to 1.2μs.                                                                                                                                                                                          |

| 4c | Minimum Off-<br>Time                                  | 0xFE43           | [3:0]        | R/W        | Sets the minimum off-time in 80ns steps from 40ns to 1.2μs.                                                                                                                                                                                        |

|    | IBAL<br>Configuration                                 |                  | [7:0]        | R/W        | The ADP1048 provides a current balancing circuit for interleaved PFC or AC-line phase detection for bridgeless.  The IBAL feature is enabled by default and disabled only for specific debugging purposes. The IBAL gain can be set from 0 to 127. |

|    | Advanced<br>Settings                                  | 0xFE4F           | [7:0]        | R/W        | Advanced Feature Configuration                                                                                                                                                                                                                     |

| 5a | None                                                  |                  |              |            | No advanced feature is enabled.                                                                                                                                                                                                                    |

| 5b | Smart<br>Frequency<br>-Frequency<br>Select            | 0xFE4F<br>0xFE1C | [3]<br>[5:0] | R/W<br>R/W | Enables smart frequency switching at lower loads to achieve higher efficiency. The frequency value must be lower than PWM frequency.                                                                                                               |

| 5c | Synchronization<br>- Freq Division                    | 0xFE4F<br>0xFE1E | [1]<br>[1:0] | R/W<br>R/W | Enables PWM synchronization (f <sub>sw</sub> ) with an external clock source (f <sub>sync</sub> ).  Frequency division sets the ratio between f <sub>sw</sub> and f <sub>sync</sub> .                                                              |

| 5d | Frequency Dithering - Switching Frequency Update Rate | 0xFE4F<br>0xFE1D | [6:0]        | R/W        |                                                                                                                                                                                                                                                    |

| 6  | Reset                                                 |                  |              |            | Undoes uncommitted changes in simulation mode. If connected to a device, it reloads the programmed settings.                                                                                                                                       |

|    | Apply Settings                                        |                  |              |            | Applies all the PWM settings to the part.                                                                                                                                                                                                          |

analog.com Rev. B 21 of 43

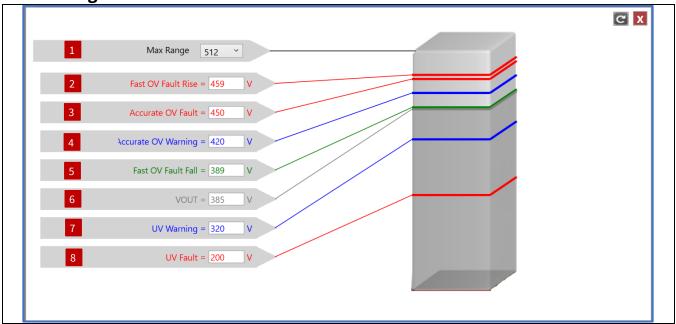

# **VFB Settings**

Figure 16. VFB Settings Navigation

### Table 15. Figure 16 Callouts

| NO. | NAME                  | REG    | BITS   | R/W                                                                                 | DESCRIPTION                                                                                                                                                                                                                                 |

|-----|-----------------------|--------|--------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | INAME                 | KLG    | ыіз    | K/VV                                                                                | DESCRIPTION                                                                                                                                                                                                                                 |

| 1   | Max Range             | 0x20   | [2:0]  | R/W                                                                                 | Sets the exponent for the output voltage. Supported Max                                                                                                                                                                                     |

|     |                       | 0x21   | [11:0] | R/W                                                                                 | Range values are 256, 512, 1024, and 2048. Ensure all other                                                                                                                                                                                 |

|     |                       | 0x40   | [10:0] | R/W                                                                                 | values are less than the Max Range selected, otherwise a                                                                                                                                                                                    |

|     |                       | 0x42   | [10:0] | R/W                                                                                 | warning message will be displayed.                                                                                                                                                                                                          |

|     |                       | 0x44   | [10:0] | R/W The output voltage value is calcula format $(V = Y * 2^{N})$ , where Y is the m | The output voltage value is calculated using a linear mode format ( $V = Y * 2^N$ ), where Y is the mantissa (lower bits), and N is the exponent in 2-s complement (upper bits or register 0x20).                                           |

| 2   | Fast OV Fault<br>Rise | 0xFE2F | [6:0]  | R/W                                                                                 | Sets the rising threshold of an analog comparator at the OVP pin input. Threshold OVP <sub>th</sub> = (register value * $0.492/128$ ) + 1.                                                                                                  |

|     |                       |        |        |                                                                                     | The equivalent voltage is based on OVP voltage divider, $V_{OVP} = OVP_{TH} * (1 + R_{UP}/R_{DOWN})$ . The default divider ratio is $384k\Omega$ and $1k\Omega$ , the minimum setting is $385V$ , and the $0x3F$ register value is $478V$ . |

|     |                       |        |        |                                                                                     | To set a value, directly input the value or use the slider. Press <i>Enter</i> to confirm value change.                                                                                                                                     |

| 3   | Accurate OV<br>Fault  | 0x20   | [2:0]  | R/W                                                                                 |                                                                                                                                                                                                                                             |

analog.com Rev. B 22 of 43

|   | Exponent N               | 0x40   | [10:0] | R/W | Sets the accurate overvoltage threshold measured at the PFC output, which triggers an overvoltage fault condition.                    |

|---|--------------------------|--------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------|

|   | Mantissa                 |        |        |     | output, which triggers an overvoltage fault condition.                                                                                |

|   | Accurate OV<br>Hyst      | 0x20   | [2:0]  | R/W | Sets the hysteresis for VOUT_OV_FAULT condition. The register value is the difference between OV Fault and OV Hyst                    |

|   | Exponent N               | 0xFE50 | [7:0]  | R/W | values . Hysteresis only applies when the disable output option is selected as VOUT_OV_FAULT_RESPONSE. See the Flag Settings section. |

|   | Mantissa                 |        |        |     | The PFC output is enabled when the output voltage is lower than the VOUT_OV_LIMIT minus this hysteresis.                              |

| 4 | Accurate OV<br>Warning   | 0x20   | [2:0]  | R/W | Sets the accurate overvoltage threshold measured at the PFC output that causes an overvoltage warn condition.                         |

|   | Exponent N<br>Mantissa   | 0x42   | [10:0] | R/W |                                                                                                                                       |

| 5 | Fast OV Fault<br>Fall    | 0xFE30 | [6:0]  | R/W | Similar to Fast OV Fault Rise, this sets the falling threshold of an analog comparator at the OVP pin input.                          |

|   |                          |        |        |     | Threshold OVP <sub>TH</sub> = (register value * 0.492/128) + 1.                                                                       |

| 6 | VOUT                     | 0x20   | [2:0]  | R/W | Sets the VOUT to the commanded value.                                                                                                 |

|   | Exponent N               |        |        |     |                                                                                                                                       |

|   | Mantissa                 | 0x21   | [11:0] | R/W |                                                                                                                                       |

| 7 | UV Warning<br>Exponent N | 0x20   | [2:0]  | R/W | Sets the accurate undervoltage threshold measured at the PFC output that triggers an undervoltage warning condition.                  |

|   | Mantissa                 | 0x43   | [10:0] | R/W |                                                                                                                                       |

| 8 | UV Fault                 | 0x20   | [2:0]  | R/W | Sets the accurate undervoltage threshold measured at the PFC output that triggers an undervoltage fault condition.                    |

|   | Exponent N<br>Mantissa   | 0x44   | [10:0] | R/W | 110 output that triggers an undervoltage radit condition.                                                                             |

analog.com Rev. B 23 of 43

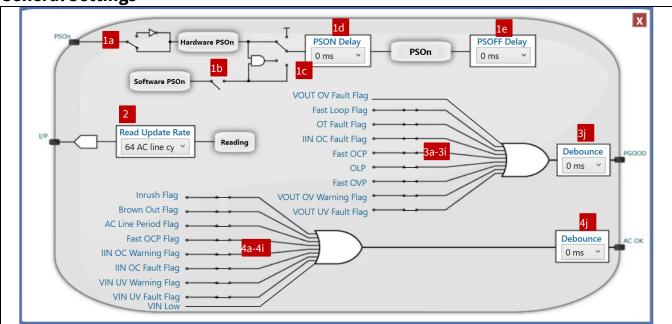

# **General Settings**

Figure 17. General Settings Navigation

#### **Table 16. Figure 17 Callouts**

| NO. | NAME                                         | REG    | BITSs | R/W | DESCRIPTION                                                                                                                                                 |

|-----|----------------------------------------------|--------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1a  | PSON Settings<br>Control Pin<br>Polarity     | 0x02   | [1]   | R/W | Sets polarity for the control pin (PSON).                                                                                                                   |

| 1b  | Operation                                    | 0x01   | [7]   | R/W | Sets the device response to the operation command.                                                                                                          |

| 1c  | PSON<br>Configuration<br>Power-Up<br>Control | 0x02   | [4:2] | R/W | Set if the device powers up when power is present or wait for enable from the control pin and/or the OPERATION command.                                     |

| 1d  | PSON Delay                                   | 0xFE06 | [3:2] | R/W | Sets the time from when the PSON signal is set to when soft start begins: 0ms, 50ms, 250ms or 1s.                                                           |

| 1e  | PSOFF Delay                                  | 0xFE06 | [1:0] | R/W | Sets the time from when the PSON signal is cleared to when device is turned off: 0ms, 50ms, 250ms, or 1s.                                                   |

| 2   | Read Update<br>Rate                          | 0xFE3A | [2:0] | R/W | Sets averaging window for the PWR current and voltage reading.  The register value is in half AC cycles while GUI is specified in AC cycles for simplicity. |

analog.com Rev. B | 24 of 43

| 3a | PGOOD Config            | 0xFE0A | [7:0] | R/W | Specifies the flags that are checked to determine the PGOOD status. |

|----|-------------------------|--------|-------|-----|---------------------------------------------------------------------|

| 3b | VOUT OV Fault<br>Flag   |        | [0]   | R/W | VOUT OV Flag is always reflected on PGOOD status.                   |

| 3c | Fast Loop Flag          |        | [1]   | R/W | If the switch is open, PGOOD ignores Fast Loop flag.                |

| 3d | OT Fault Flag           |        | [2]   | R/W | If the switch is open, PGOOD ignores Over Temperature Fault flag.   |

| 3e | IIN OC Fault Flag       |        | [3]   | R/W | If the switch is open, PGOOD ignores Input OverCurrent Fault flag.  |

| 3f | Fast OCP                |        | [4]   | R/W | If the switch is open, PGOOD ignores Fast OCP flag.                 |

| 3g | OLP                     |        | [5]   | R/W | If the switch is open, PGOOD ignores Open Loop flag.                |

| 3h | Fast OVP                |        | [6]   | R/W | If the switch is open, PGOOD ignores Fast OVP flag.                 |

| 3i | VOUT OV<br>Warning Flag | 0xFE05 | [7]   | R/W | If the switch is open, PGOOD ignores VOUT OV Warning flag.          |

| 3j | VOUT UV Fault<br>Flag   |        | [3:0] | R/W | If the switch is open, PGOOD ignores VOUT UV Fault flag.            |

|    | PGOOD<br>Debounce       |        |       |     | Sets the debounce time for PGOOD pin: 0ms, 200ms, 320ms, or 600ms.  |

|    | ACOK Config             | 0xFE0B | [7:0] | R/W | Specifies which flags are checked to determine the ACOK status.     |

| 4a | Inrush Flag             |        | [0]   | R/W | If the switch is open, ACOK ignores Inrush flag.                    |

| 4b | Brown Out Flag          |        | [1]   | R/W | If the switch is open, ACOK ignores Brown Out flag.                 |

| 4c | AC Line Period<br>Flag  |        | [2]   | R/W | If the switch is open, ACOK ignores AC Line Period flag.            |

| 4d | Fast OCP Flag           |        | [3]   | R/W | If the switch is open, ACOK ignores Fast OCP flag.                  |

| 4e | IIN OC Warning<br>Flag  |        | [4]   | R/W | If the switch is open, ACOK ignores Input OC Warning flag.          |

|    |                         |        | I     | l   |                                                                     |

analog.com Rev. B 25 of 43

|    | 1                      |        |       |     |                                                                       |

|----|------------------------|--------|-------|-----|-----------------------------------------------------------------------|

| 4f | IN OC Fault Flag       |        | [5]   | R/W | If the switch is open, ACOK ignores Input OC Fault flag.              |

| 4g | VIN UV Warning<br>Flag |        | [6]   | R/W | If the switch is open, ACOK ignores VIN UV Warning flag.              |

| 4h | VIN UV Fault<br>Flag   | 0xFE05 | [7]   | R/W | If the switch is open, ACOK ignores the AC Line Period flag.          |

| 4i | VIN OFF                |        |       |     | The VIN_OFF flag is always reflected in the ACOK status.              |

| 4j | ACOK Debounce          |        | [7:4] | R/W | Sets the debounce time for the ACOK pin: 0ms, 200ms, 320ms, or 600ms. |

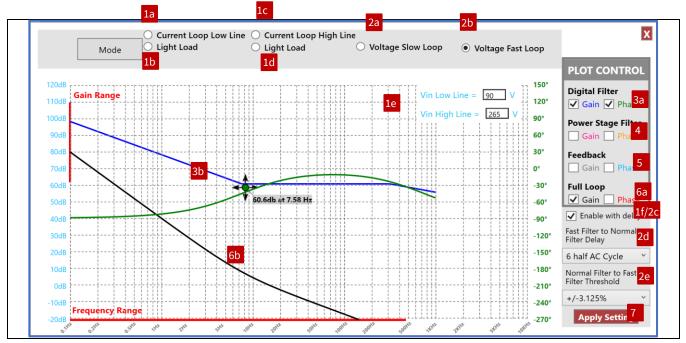

# **Filter Settings**

Figure 18. Filter Settings Navigation

#### Table 17. Figure 18 Callouts

| NO. | NAME                         | REG | BITS | R/W | DESCRIPTION                                                                                                                                      |

|-----|------------------------------|-----|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Current-Loop<br>Compensators |     |      |     | Four compensators/filters are provided to optimize the circuit's THD response.  Configure the low-power threshold in the <i>Power Settings</i> . |

analog.com Rev. B | 26 of 43

|           |                                          | 1                |                |            |                                                                                                                                             |

|-----------|------------------------------------------|------------------|----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1a        | Current-Loop<br>Low Line                 | 0xFE29<br>0xFE2A | [7:0]<br>[7:0] | R/W<br>R/W | Sets the current-loop filter gain for low-line input. Sets the current-loop filter zero for low-line input.                                 |

| 1b        | Current-Loop<br>Low Line Light<br>Load   | 0xFE90<br>0xFE91 | [7:0]<br>[7:0] | R/W<br>R/W | Sets the current-loop filter gain for low-line input and light load.  Sets the current-loop filter zero for low-line input and light        |

|           |                                          |                  |                |            | load.                                                                                                                                       |

| 1c        | Current-Loop<br>High Line                | 0xFE2B<br>0xFE2C | [7:0]<br>[7:0] | R/W<br>R/W | Sets the current-loop filter gain for high-line input. Sets the current-loop filter zero for high-line input.                               |

|           |                                          |                  | []             | .,         | Sets the edirent toop inter zero for high time input.                                                                                       |

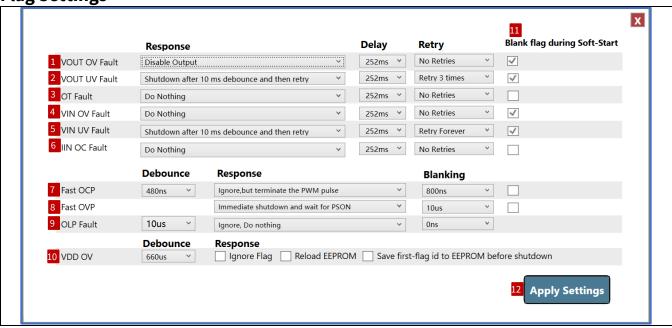

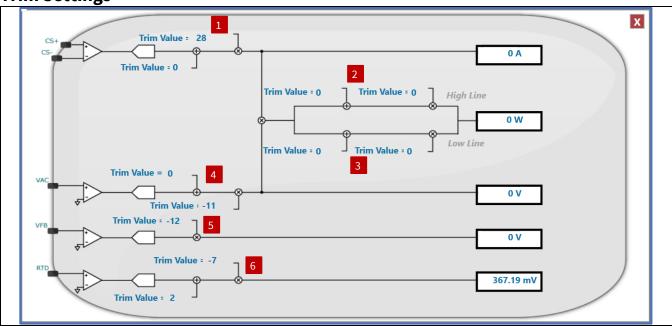

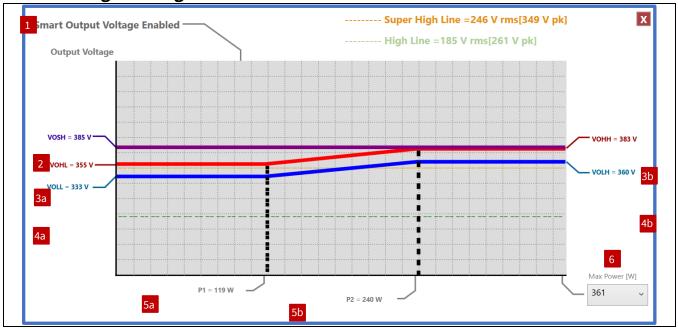

| 1d        | Current-Loop<br>High Line Light          | 0xFE92<br>0xFE93 | [7:0]<br>[7:0] | R/W<br>R/W | Sets the current-loop filter gain for low-line input and light load.                                                                        |